페이지 테이블

페이지 테이블 엔트리(PTE)

- present/absent bit: 해당 PTE의 사용 여부를 나타냄

- reference bit: 해당 페이지가 접근된 적이 있는지

- modify bit(dirty): 해당 페이지값이 변경된 적이 있는지

- protection bit: read/write/execute 등 어떤 작업들이 허용되는지를 나타냄

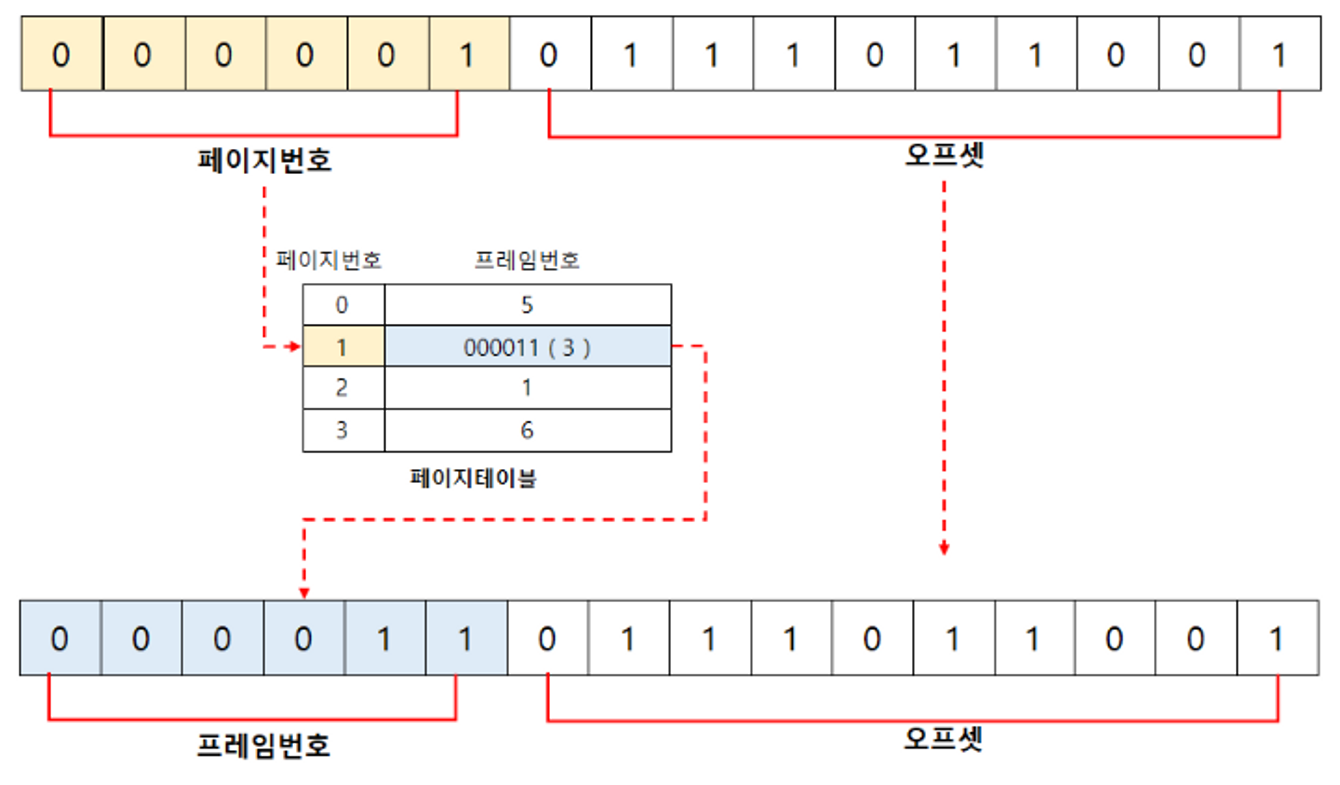

VPN, PFN

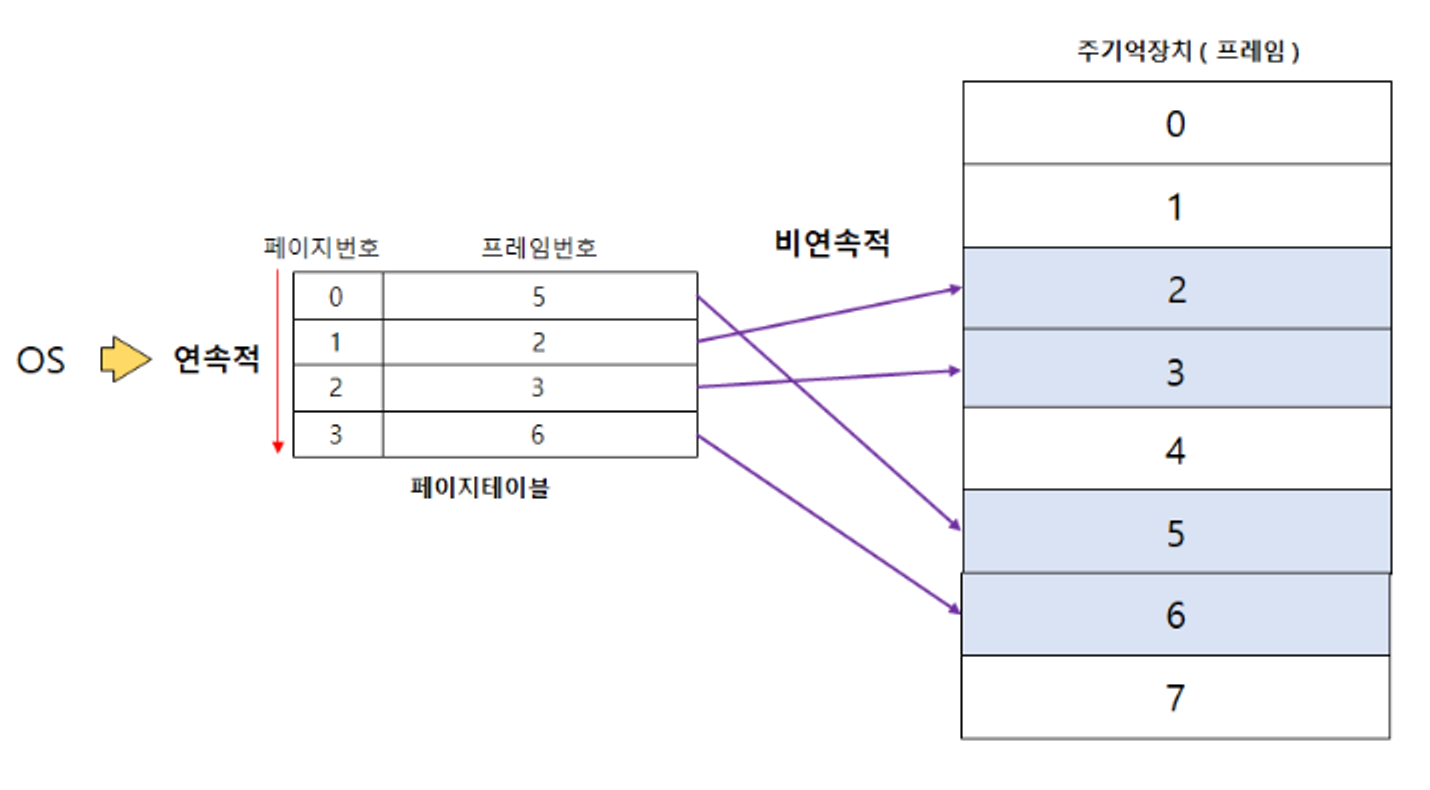

- 페이지 테이블은 프로세스가 가질 수 있는 페이지의 개수만큼 주소 변환 엔트리를 가짐

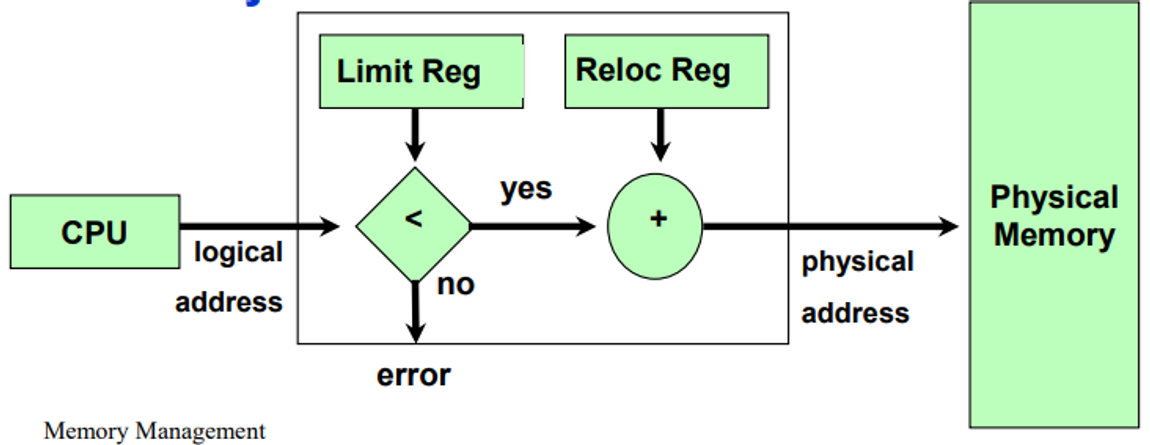

- 논리 주소는 VPN(Virtual Page Number)와 offest으로 구성

- PTE에는 PFN(Page Frame Number)를 저장하고 있으며, 물리주소는 PFN+offset이 됨

- VPN은 페이지 테이블을 위한 인덱스일 뿐임

페이징의 단점

- 내부 단편화는 여전히 존재함

- 2번의 메모리 접근으로 인한 속도 저하 ⇒ TLB가 등장

- 페이지 테이블도 DRAM에 저장되어 있음

- 결국 (1)페이지 테이블과 (2)실제 물리 주소 와 같이 2번 접근이 필요

- 한 프로세스당 하나의 페이지 테이블이 존재하고, 한 주소당 하나의 PTE를 사용하기 때문에 테이블에 해당하는 용량이 많아질 수 있음

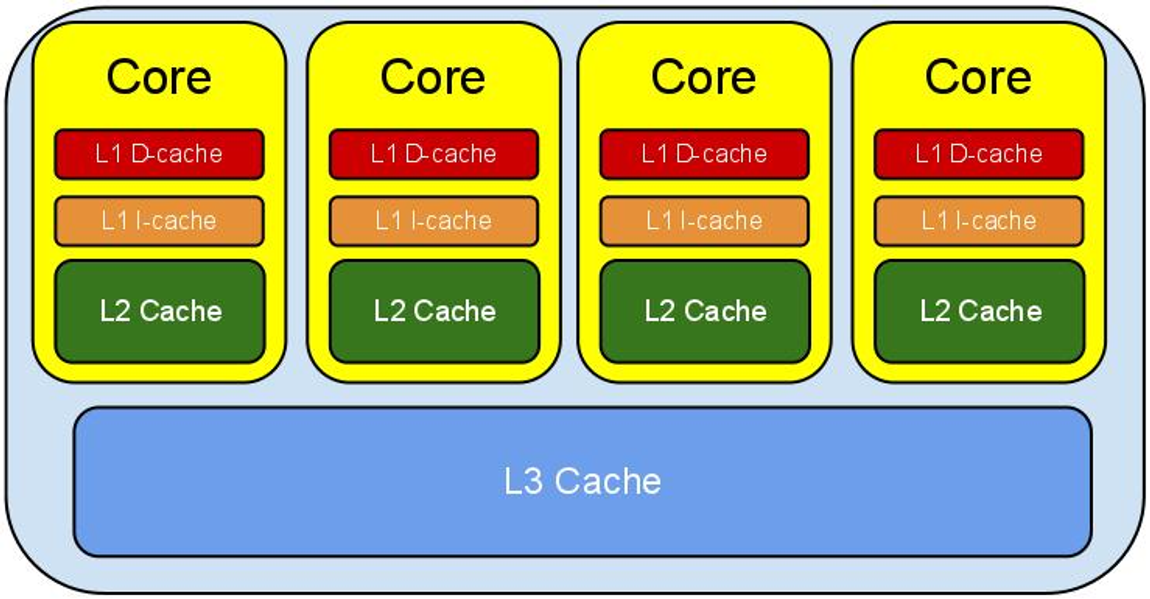

TLB(Translation Lookaside Buffer)

MMU with TLB

- TLB란 MMU에 소속된 칩으로, 메모리와 CPU 사이에 있는 주소 변환을 위한 캐시

- 페이지 테이블에 있는 리스트를 보관하며 CPU가 페이지 테이블까지 가지 않도록 해 속도를 향상시킬 수 있는 캐시 계층임

- 자주 참조되는 가상-물리주소 변환 정보를 저장

TLB의 문제점

- TLB 정보는 이를 탑재시킨 프로세스에서만 유효함

- 즉, 다른 프로세스가 동작할 때는 필요없는 정보가 TLB에 남게됨

단점 해결 방법

- 프로세스 context switching 시 TLB를 비우기

- 빈번하게 발생할 경우 성능에 부담이 됨

- TLB 내에 프로세스를 식별하기 위한 주소 공간 식별자 필드를 추가

- ASID(Address Space Identifier) 라고 함

- 각각의 task마다 ID를 고유로 부여하며 이를 ASID에 표시하여 저장

페이지 테이블의 종류

Multilevel(Hierarchy) Page Table

- 페이지 테이블 자체가 다시 페이징되는 것

- 메모리 이슈가 덜해지지만 레이어가 많아진다면 메모리 접근에 대한 오버헤드 이슈가 생길 가능성이 있음

- 64bit 구조에서 계층적 페이지 테이블이 부적합한 이유

Hashed Page Table

- 각 항목은 연결 리스트를 가지고 있고, 해시 원소는 세 개의 필드(가상 페이지 번호, 매핑 프레임 번호, 다음 주소)를 가짐

- 논리적 주소 공간의 페이지 번호인 p를 해시한 결과값으로 테이블을 검사한 뒤, 해당 물리적 메모리를 찾아가게 됨

- 64bit 시스템에서는 클러스터형 페이지 테이블을 사용함

- 해시형 페이지에서 각 항목들이 한 개의 페이지만 가리키는 대신 각 항목들이 여러 개의 페이지를 가리키는 방식

- 따라서 한 개의 페이지 테이블 항목이 여러 페이지 프레임에 대한 매핑 정보를 지닐 수 있음

- 메모리 접근이 불연속적이면서 전 주소 공간으로 넓게 퍼져 나오는 경우에 유용

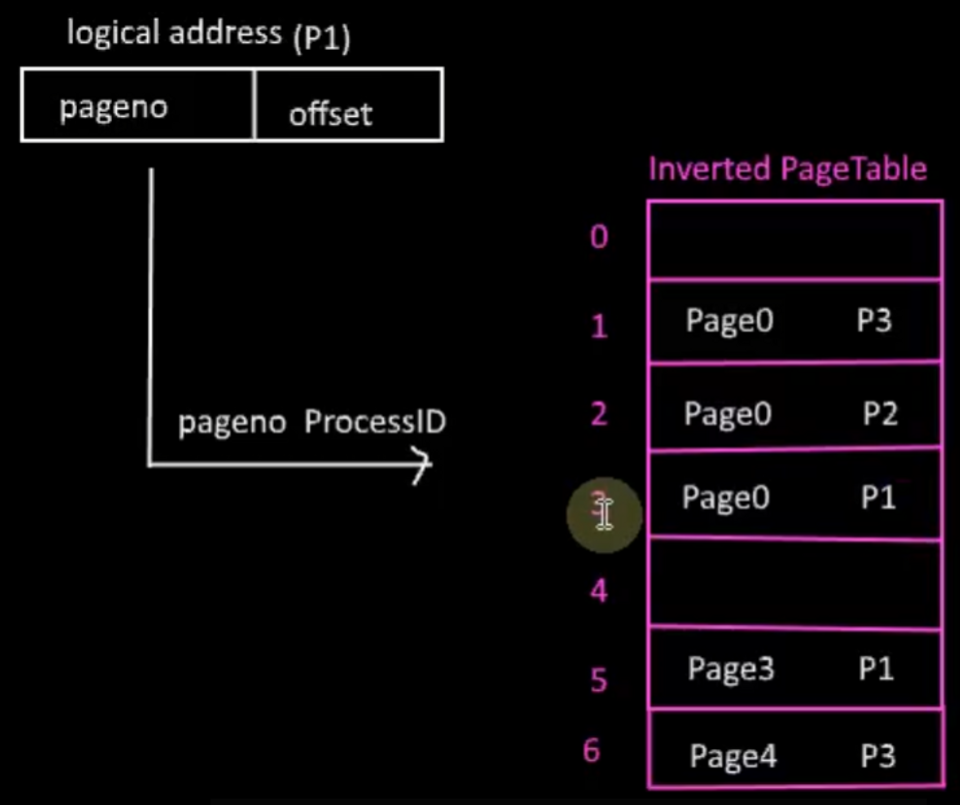

Inverted Page Table의 특징

- 기존 페이지 테이블

- 보통 프로세스는 각자 하나씩 페이지 테이블을 가짐

- 각 페이지 테이블 항목의 개수가 너무 많아질 수 있다는 단점이 있음

- 역페이지 테이블

- 논리적 주소가 아니라 물리적 메모리 주소 입장에서 만들어진 테이블 구조

- 각 메모리 프레임마다 할당하여 페이지 테이블의 엔트리 개수 = 메모리 프레임의 수

- 시스템에는 단 하나의 페이지 테이블만이 존재하여 메모리에서 훨씬 작은 공간을 점유

- 몇 번째 프레임인지에 대한 정보가 아니라, 프로세스의 번호 pid를 저장

Inverted Page Table의 주소 계산 방법

- 기존 테이블들의 경우에는 pageno를 인덱스로 하여 페이지 테이블에 바로 접근했지만, 역페이지 테이블의 경우 전체 테이블의 항목을 서치하며 해당 데이터와 일치하는 값을 찾아야 함

- 따라서 메모리를 절약하는 대신, 탐색 시간이 오래걸릴 수 있다는 단점이 존재

⇒ 여기에 해시 테이블을 추가로 사용해 탐색 개수를 줄일 수 있음

Inverted 방식의 단점

- 메모리 공유 불가

- 모든 페이지와 프레임은 일대일 대응 관계이므로 프로세스간 메모리 공유가 불가능

- 같은 프로세스 안에서도 페이지가 다르면 데이터 공유가 불가능

- 페이지 테이블 참조 오버헤드

- 주소의 매핑은 매우 빈번하게 일어나는데, 그때마다 테이블에서 pid/p 값을 찾아야함

- 최악의 경우 페이지 테이블의 끝까지 탐색해야 하기 때문에 오버헤드가 굉장히 심함

- 프로세스마다 페이지 테이블을 가지는 경우 페이지 테이블의 인덱스는 논리적 주소의 page#와 동일하기 때문에 바로 접근할 수 있지만, 역페이지 방식의 경우 메모리의 프레임 위치기 때문에 논리적 주소로 바로 접근이 불가능함

References

'Computer Science > 운영체제' 카테고리의 다른 글

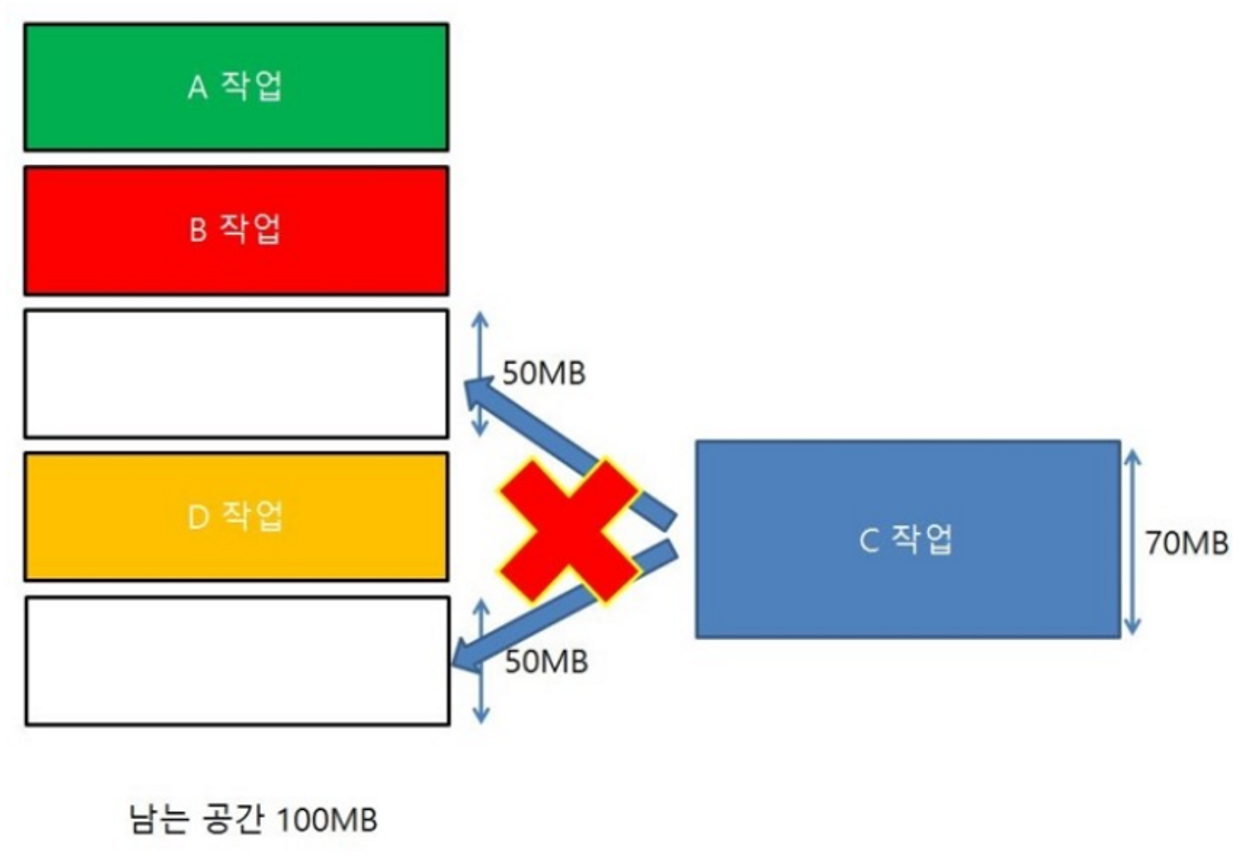

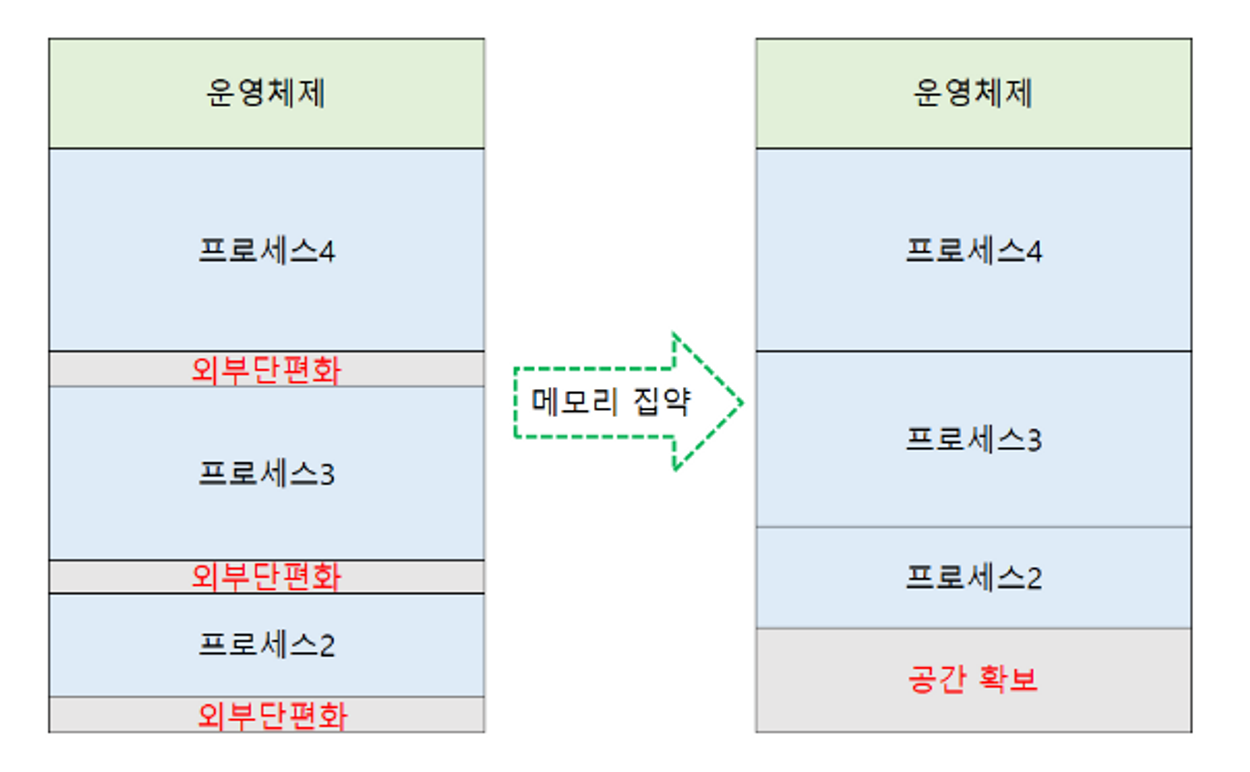

| [운영체제] 메모리 분할(연속/불연속 할당, 단편화) (0) | 2023.03.14 |

|---|---|

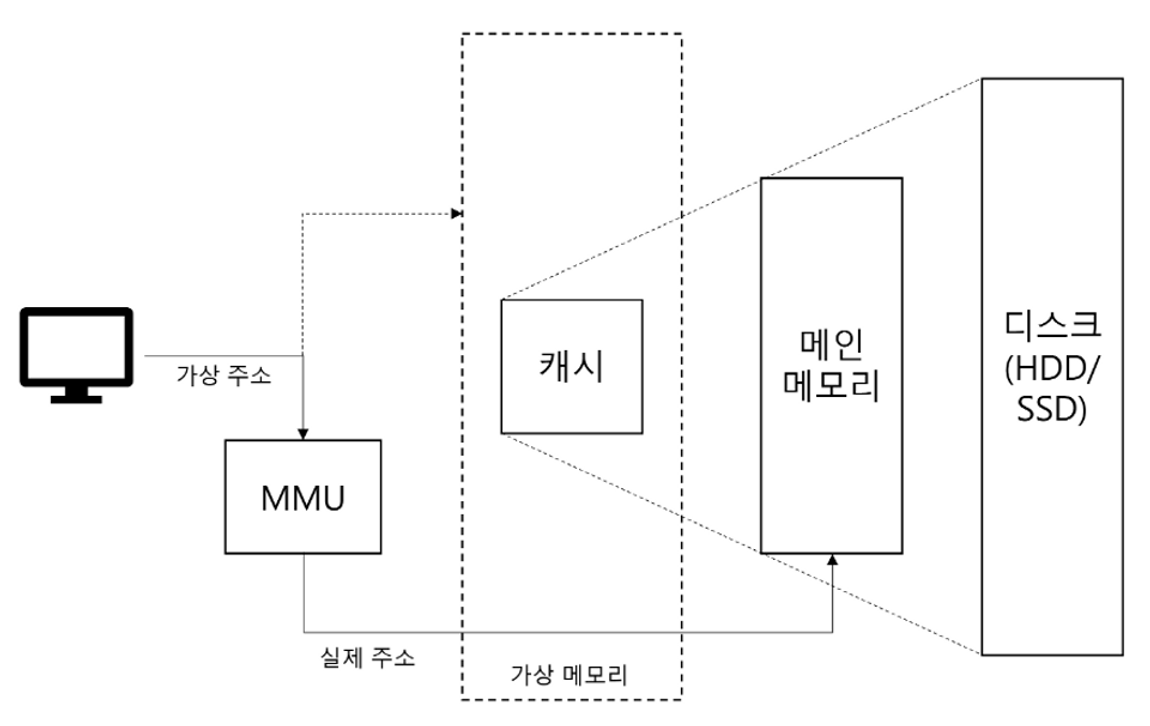

| [운영체제] 가상 메모리, 스와핑, 페이지 폴트 (0) | 2023.03.13 |

| [운영체제] 메모리 계층(캐시히트, 지역성, 캐시 매핑) (0) | 2023.03.13 |

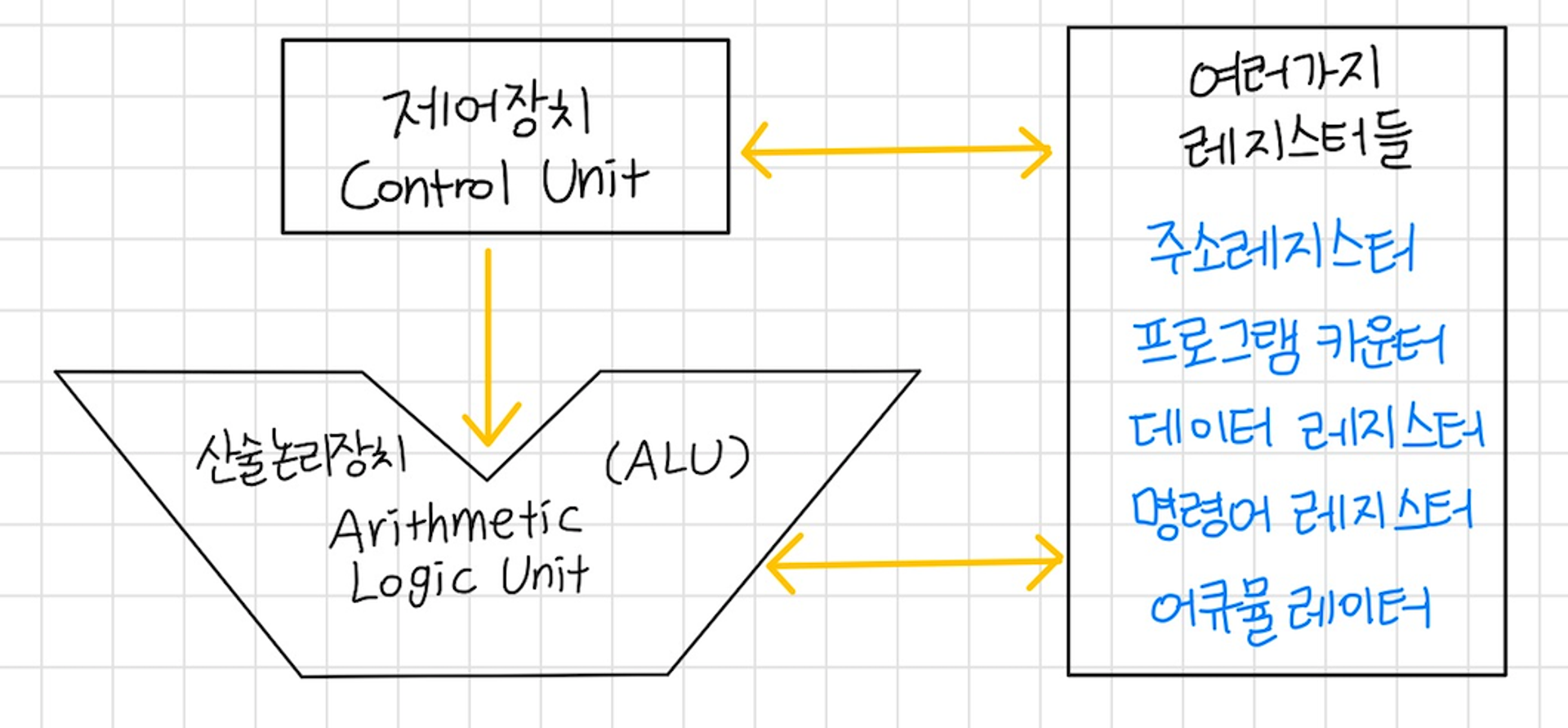

| [운영체제] 컴퓨터 하드웨어의 구성 요소(CPU, 메모리, 시스템 버스) (0) | 2023.03.12 |

| [운영체제] 운영체제란?(운영체제의 구조, 시스템콜) (0) | 2023.03.11 |